onsemi (Ansemi)

이미지는 예시일 수 있습니다.

제품 세부사항은 사양을 확인하세요.

제품 세부사항은 사양을 확인하세요.

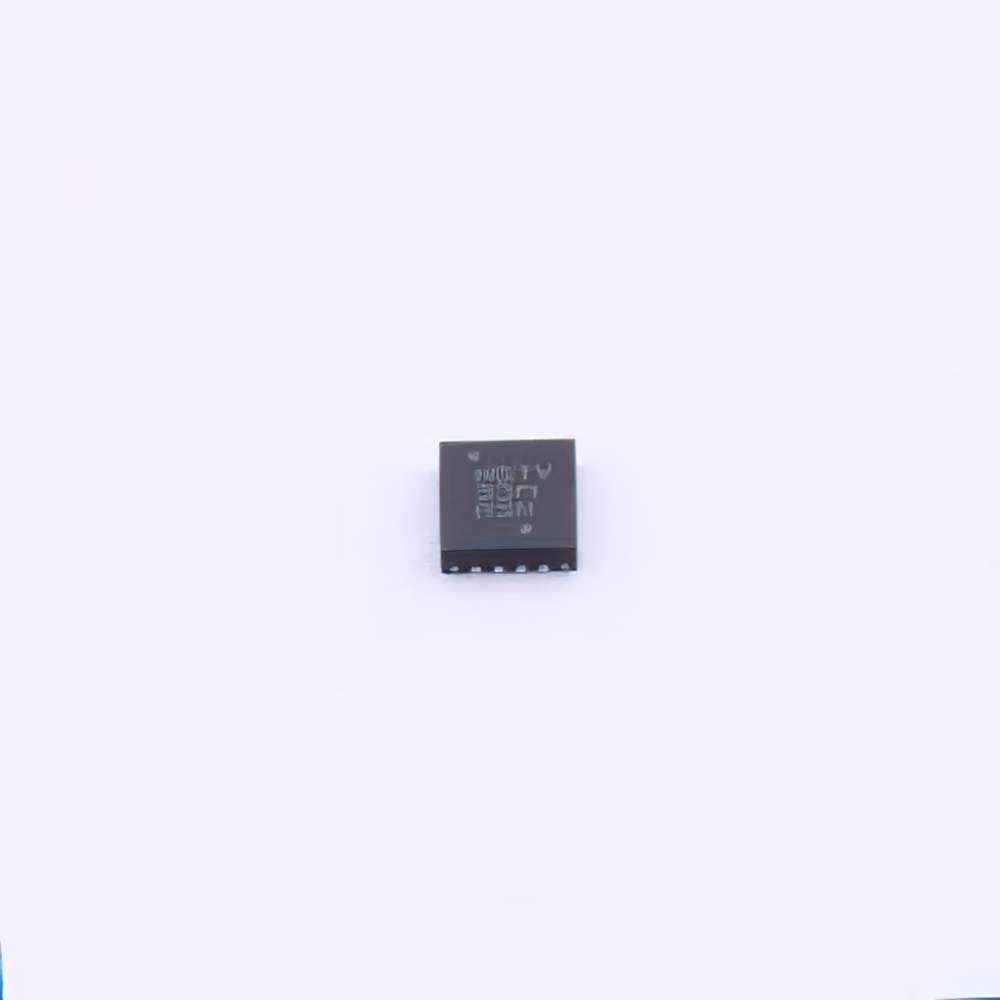

NB7VQ1006MMNTXG

6 differential CML outputs

부품 번호

NB7VQ1006MMNTXG

범주

Logic Devices > Special Logic ICs

제조사/브랜드

onsemi (Ansemi)

캡슐화

QFN-24-EP(4x4)

포장

taping

패키지 수

3000

설명하다

The NB7VQ1006M is a high performance equalizer receiver (signal booster) operating at a maximum speed of 10 Gbps/7.5 GHz from a 1.8 V or 2.5 V supply. When placed in series in the data/clock path, the receiver will amplify the degraded signal traveling in the FR4 backplane or cable interconnect and output six identical CML copies of the input signal. An equalizer enable pin (EQEN) allows the IN/IN input to flow through or bypass the equalizer section. The equalizer function can be controlled by setting EQEN. When EQEN is set low, the IN/IN input bypasses the equalizer. When EQEN is set high, the IN/IN input flows through the equalizer. The default state at startup is low. The differential data/clock inputs are in a 100 Ω center-tapped configuration combined with a pair of internal 50 Ω termination resistors through the VT pin and accept LVPECL, CML, or LVDS logic levels. This feature provides on-chip transmission line termination at the receiver side, requiring no external components. The NB7VQ1006M is a member of the PEEQ GigaComm series of high-performance data/clock products.

견적요청

모든 필수 필드를 작성하고 제출을 클릭하세요. 12시간 이내에 이메일로 연락드리겠습니다. 질문이 있으신 경우 [email protected] 에게 메시지를 남기거나 이메일을 보내주시면 최대한 빨리 답변해 드리겠습니다.

재고 83201 PCS

연락처 정보

키워드NB7VQ1006MMNTXG

NB7VQ1006MMNTXG 전자 부품

NB7VQ1006MMNTXG 매상

NB7VQ1006MMNTXG 공급자

NB7VQ1006MMNTXG 유통 업체

NB7VQ1006MMNTXG 데이터 테이블

NB7VQ1006MMNTXG 사진

NB7VQ1006MMNTXG 가격

NB7VQ1006MMNTXG 권하다

NB7VQ1006MMNTXG 최저 가격

NB7VQ1006MMNTXG 찾다

NB7VQ1006MMNTXG 구매

NB7VQ1006MMNTXG 칩숏